# DCM FLYBACK CONVERTER LED DRIVER DESIGN

# **Final Project Report**

Siddhanth Toranagatti

University of Colorado Boulder

ECEN5527 - Power Electronics Project Laboratory

December 2025

# **EXECUTIVE SUMMARY**

This report documents the complete design, implementation, and testing of a 24W DCM flyback converter LED driver. The project encompasses comprehensive design calculations, PCB layout, transformer construction, and extensive debugging efforts.

# **Design Specifications:**

- Input: 85-265 VAC (universal input range)

- Output: 20V, 0-1.2A (0-24W)

- Switching frequency: 100 kHz maximum

- Control: UCC28740 primary-side regulation controller

- Operating mode: DCM (Discontinuous Conduction Mode)

- Galvanic isolation for safety compliance

# **Project Timeline and Challenges:**

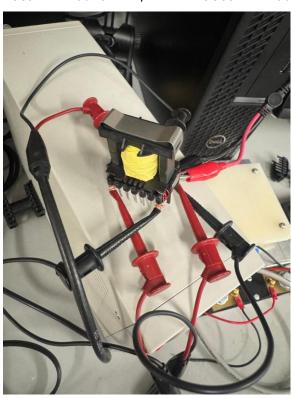

This project encountered significant challenges during the implementation phase. The initial PCB order experienced a critical routing error with the auxiliary winding connection, requiring a complete board redesign and reorder. This delay compressed the testing timeline considerably. Upon receiving the corrected boards, I completed full population and soldering within 32 hours, working overnights in the laboratory to meet project deadlines.

During initial testing, the converter exhibited complete failure of MOSFET switching operation. Despite the primary-side circuitry appearing functional, the power MOSFET would not switch under any conditions. The secondary-side feedback circuit also showed anomalous behavior. This necessitated systematic debugging including multiple component replacements, verification of all passive values, testing of multiple snubber configurations, and detailed voltage measurements at all critical nodes.

Due to the compressed timeline and persistent hardware issues, I was only able to complete open-loop characterization tests. The closed-loop operation with full CV/CC regulation remains incomplete pending resolution of the switching malfunction.

# 1. INTRODUCTION AND TOPOLOGY SELECTION

# 1.1 Project Overview

This project focuses on the design and implementation of a flyback converter-based LED driver capable of operating from universal AC mains input (85-265 VAC). The converter provides constant current/constant voltage (CC/CV) regulation suitable for driving LED loads up to 24W.

LED drivers present unique design challenges compared to traditional DC-DC converters. They must provide precise current regulation to ensure consistent LED brightness and longevity, while also implementing voltage regulation to prevent LED overvoltage damage. The wide input voltage range requirement adds complexity to the transformer design and control strategy.

# 1.2 Topology Selection

# 1.2.1 Topologies Considered

# **Flyback Converter:**

# Advantages:

- Single switch simplicity reduces component count and cost

- Provides inherent galvanic isolation required for safety compliance

- Natural energy storage in transformer enables excellent wide input range operation

- · Simple current regulation through primary-side sensing

- Minimal output filtering requirements

- Cost-effective for power levels below 100W

## Disadvantages:

- Higher peak currents and voltages stress components

- Transformer stores energy requiring larger magnetic core

- Limited practical power output (<150W typically)</li>

- Requires careful snubber design to handle leakage inductance energy

- Higher EMI generation compared to forward converters

# **Forward Converter:**

# Advantages:

- Lower component stress with continuous energy transfer

- Higher efficiency at higher power levels

- Transformer operates as true transformer rather than coupled inductor

- Better suited for multiple output voltages

# Disadvantages:

- Requires additional reset winding and components increasing complexity

- Higher component count increases cost

- Less suitable for wide input voltage range

- · More complex current regulation

# 1.2.2 Selected Topology: DCM Flyback Converter

The flyback topology operating in Discontinuous Conduction Mode (DCM) was selected as optimal for this application based on several key factors:

- Power Level Match: At 24W, the flyback converter operates in its sweet spot where it offers excellent efficiency and minimal complexity

- Wide Input Range: The energy storage mechanism of the flyback naturally accommodates the 3:1 input voltage range without requiring complex compensation

- Safety Isolation: The flyback transformer provides the required galvanic isolation between mains input and low-voltage LED output

- Current Regulation: DCM operation enables precise current regulation through simple peak current mode control

- Component Count: Single-switch topology minimizes component count, reducing cost and board area

# 1.3 Control Strategy

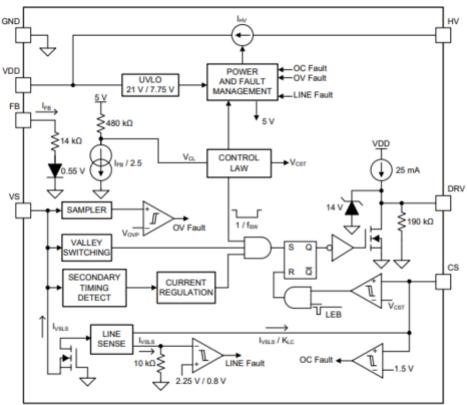

## 1.3.1 Control IC Selection: UCC28740

The UCC28740 from Texas Instruments was selected as the control IC. This device is specifically designed for flyback LED drivers and offers several advantages:

- Primary-Side Regulation (PSR): Eliminates need for optocoupler feedback circuit, reducing component count and improving reliability

- Constant Current / Constant Voltage: Built-in algorithms provide both CC and CV regulation modes with smooth transition

- Valley Switching: Reduces switching losses by turning on the MOSFET at valley points of the drain voltage oscillation

- Frequency Modulation: Variable switching frequency optimizes efficiency across load range while reducing EMI

- Protection Features: Comprehensive overvoltage, overcurrent, and overtemperature protection integrated

- Line Compensation: Built-in line regulation improves output accuracy across wide input range

# 2. POWER STAGE DESIGN

# 2.1 Input Stage Design

# 2.1.1 Input Specifications and Rectification

The input stage converts universal AC mains voltage to a DC bulk voltage. Key parameters:

- Input voltage range: 85-265 VAC RMS

- Minimum bulk voltage: Vbulk min = √2 × 85V = 120V DC

- Maximum bulk voltage: Vbulk max =  $\sqrt{2}$  × 265V = 375V DC

- Bulk voltage range: 3.1:1 (120V to 375V)

A full-bridge rectifier configuration was selected using four 1N4007 diodes providing 1000V reverse voltage rating and 1A average forward current capability.

# 2.1.2 Bulk Capacitor Selection

Required capacitance calculation:

```

Cbulk = (2 \times Pout \times thold) / (Vbulk min^2 - Vbulk ripple^2)

```

Where thold = 8.33ms (half line cycle at 60Hz) and allowing 20% voltage ripple:

```

Cbulk = (2 \times 24W \times 8.33ms) / (120^2 - 96^2) = 150\mu F minimum

```

Selected: 220µF, 450V electrolytic capacitor (50% design margin)

## 2.2 Transformer Turns Ratio Selection

The transformer turns ratio is critical for proper voltage stress on the power MOSFET:

```

Vreflected = Nps × (Vout + Vf)

VDS max = Vbulk max + Vreflected + Vleakage spike

```

For a 650V rated MOSFET with 80% derating:

```

Vrated derated = 0.8 \times 650V = 520V

```

Allowing margin for leakage inductance spike, selected Vreflected = 100V:

```

Nps = Vreflected / (Vout + Vf) = 100V / (20V + 0.6V) = 4.85

```

Selected: **Nps = 5:1** (rounded to practical value), providing Vreflected = 103V

# 2.3 Primary Inductance Selection

The primary inductance determines peak current and energy storage capability:

```

Ipk = \sqrt{(2 \times Pin / (Lp \times fsw))}

```

Where Pin = Pout/ $\eta$  = 24W/0.85 = 28.2W. Targeting lpk  $\approx$  1.5A for reasonable current stress:

```

Lp = 2 \times 28.2W / (1.5^2 \times 100kHz) = 251\mu H

```

Selected:  $Lp = 250\mu H$

# 2.4 Maximum Duty Cycle

Maximum duty cycle occurs at minimum input voltage and maximum load:

```

Dmax = (Nps \times Vout) / (Vbulk_min + Nps \times Vout)

Dmax = (5 \times 20.6V) / (120V + 103V) = 0.46 (46%)

```

This duty cycle is well within the practical range for DCM flyback operation.

# 3. TRANSFORMER DESIGN

# 3.1 Core Selection

## 3.1.1 Area Product Method

The transformer core size was determined using the area product (AP) method:

```

AP = (Lp \times Ipk \times Irms \times 10^4) / (Bmax \times Ku \times fsw)

```

Where Lp=250µH, lpk=1.43A, lrms=0.63A, Bmax=0.3T, Ku=0.4, fsw=110kHz:

```

AP = (250\mu H \times 1.43A \times 0.63A \times 10^4) / (0.3T \times 0.4 \times 110kHz) = 0.00017 cm^4

```

## 3.1.2 Core Selection: EE19

Based on area product calculation, an EE19 core was selected:

- Core type: EE19 (also known as EPC19)

- Material: PC40 ferrite (TDK) suitable for 100-200kHz

- Effective area (Ae): 23.6 mm<sup>2</sup> = 0.236 cm<sup>2</sup>

- Window area (Aw): 21.4 mm<sup>2</sup> = 0.214 cm<sup>2</sup>

- Volume (Ve): 1,140 mm³ = 1.14 cm³

- Mean length (le): 48.3 mm

# 3.2 Winding Design

# 3.2.1 Primary Winding

Selected Np = 40 turns for practical hand-winding. Wire gauge selection:

```

Awire = Irms / J = 0.63A / 4 A/mm^2 = 0.158 mm^2

```

Selected: AWG 25 wire (0.162 mm<sup>2</sup>, current density = 3.9 A/mm<sup>2</sup>)

## 3.2.2 Secondary Winding

Number of turns from turns ratio:

```

Ns = Np / Nps = 40 / 5 = 8 turns

```

Secondary current calculations:

```

Ipk_sec = Ipk_pri × Nps = 1.43A × 5 = 7.15A

Irms sec = 3.4A (calculated for DCM conduction)

```

Selected: 5 strands of AWG 26 in parallel (total 0.81 mm<sup>2</sup>)

# 3.2.3 Auxiliary Winding

The auxiliary winding provides bias power to the UCC28740:

```

Vaux = 12V (target for VDD supply)

Na = Np \times (Vaux / Vout) / Nps = 40 \times (12/20) / 5 = 4.8 turns

```

Selected: Na = 5 turns (rounded up), Wire: AWG 28

# 3.3 Air Gap Calculation

Required inductance factor (AL value):

```

AL = Lp / Np^2 = 250\mu H / 1600 = 156 nH/turn^2

```

Air gap length calculation:

```

lg \approx 0.4\pi \times Ae \times Np^2 / (Lp × 10^6) = 0.47 mm per gap

```

Total gap = 0.94 mm (implemented using combination of 0.23mm and 0.12mm gap sheets)

# 3.4 Window Fill Factor Analysis

Bobbin window area: 21.4 mm<sup>2</sup>. Component areas:

- Primary winding (40T, AWG 25): 7.69 mm²

- Auxiliary winding (5T, AWG 28): 0.51 mm²

- Insulation layers: 3.6 mm<sup>2</sup>

- Secondary winding (8T, 5×AWG26): 6.28 mm<sup>2</sup>

- Margin tapes: 2.4 mm²

Total =  $20.48 \text{ mm}^2$ , Fill factor = 20.48 / 21.4 = 96%

# 4. CONTROL LOOP DESIGN

# **4.1 Control System Overview**

The UCC28740 implements two independent control loops: Constant Voltage (CV) Loop regulating output voltage through TL431 and optocoupler feedback, and Constant Current (CC) Loop regulating output current through primary-side current sensing.

# 2.2 Detailed Functional Block Diagram and schematic with calculated values in the below sections:

Copyright © 2017, Texas Instruments Incorporated

\_\_\_\_\_

## CONSTANT VOLTAGE LOOP

Vout  $\rightarrow$  Voltage Divider  $\rightarrow$  TL431 Shunt Reg  $\rightarrow$  Optocoupler  $\rightarrow$  FB Pin RFB1, RFB2 VREF=2.5V PC817 UCC28740

# CONSTANT CURRENT LOOP

Iprimary  $\rightarrow$  Rcs  $\rightarrow$  CS Pin  $\rightarrow$  Internal CC Control  $\rightarrow$  Peak Current Limit  $1\Omega$  UCC28740 VCCR=0.33V Modulation

DC ANALYSIS COMPLETE DIAGRAM

**CURRENT LOOP**

VOLTAGE LOOP

# **4.2 Constant Current Loop Design**

The primary-side current is sensed through a  $1\Omega$  resistor. Output current regulation:

```

\label{eq:lout_CC} \begin{split} \text{Iout\_CC} &= (\text{Vccr} \times \text{Nps} \times \eta\_\text{xfmr}) \ / \ (2 \times \text{Rcs}) \\ \text{Where Vccr=0.33V, Nps=5, } \eta\_\text{xfmr=0.85, Rcs=1}\Omega; \\ \text{Iout CC} &= (0.33\text{V} \times 5 \times 0.85) \ / \ (2 \times 1\Omega) \ = 0.70\text{A} \end{split}

```

# 4.3 Constant Voltage Loop Design

Voltage regulation uses TL431 shunt regulator with PC817 optocoupler. Output voltage divider:

```

Vout = VREF × (1 + RFB1/RFB2)

For 20V output with VREF=2.5V:

RFB1/RFB2 = (20V / 2.5V) - 1 = 7

Selected: RFB2 = 2.4k\Omega, RFB1 = 16k\Omega (provides Vout = 19.17V)

```

# 4.4 Small-Signal AC Analysis

For DCM flyback converter with peak current mode control:

```

Gvd(s) = Gdo \times [1 - s/\omega z RHP] \times [1 + s/\omega z ESR] / [1 + s/(Qp\times\omega p) + s^2/\omega p^2]

```

Key parameters at maximum load:

DC Gain: Gdo = 40.1 dB

RHP Zero: fz\_RHP = 26.3 kHzESR Zero: fz\_ESR = 4.7 kHz

Double Pole: fp = 47.5 kHz

```

• DC Gain: Gdo = (2×Vout×Rload)/(Nps×Rcs×Re)

```

- RHP Zero: ωz\_RHP = (2×Rload)/(Lp×D²)

- ESR Zero: ωz\_ESR = 1/(Resr×Cout)

- Double Pole: ωp = π×fsw

- Quality Factor: Qp ≈ 1.5 (for DCM)

- Effective Resistance: Re = Rcs + Ron\_FET

## 2.2 Parameter Calculations for Four Corners

#### Corner 1: Low Line, Maximum Load (85VAC, 1.2A)

```

Vbulk_min = 119V

D = 0.45

fsw = 95kHz

Rload = 16.7\Omega

Gdo = (2\times20\times16.7)/(6\times1\times1.1) = 101 = 40.1dB

fz_RHP = (2\times16.7)/(2\pi\times100\mu\times0.45^2) = 26.3kHz

fz_ESR = 1/(2\pi\times0.05\times680\mu) = 4.7kHz

fp = 47.5kHz

```

## Corner 2: Low Line, Minimum Load (85VAC, 0.12A)

```

Vbulk_min = 119V

D = 0.25

fsw = 35kHz

Rload = 167\Omega

Gdo = (2\times20\times167)/(6\times1\times1.1) = 1010 = 60.1dB

fz_RHP = (2\times167)/(2\pi\times100\mu\times0.25^2) = 849kHz

fz_ESR = 4.7kHz (unchanged)

fp = 17.5kHz

```

## Corner 3: High Line, Maximum Load (265VAC, 1.2A)

```

Vbulk_max = 375V

D = 0.20

fsw = 100kHz

Rload = 16.7\Omega

Gdo = (2\times20\times16.7)/(6\times1\times1.1) = 101 = 40.1dB

fz_RHP = (2\times16.7)/(2\pi\times100\mu\times0.20^2) = 133kHz

```

```

fz_{ESR} = 4.7kHz

fp = 50kHz

```

## Corner 4: High Line, Minimum Load (265VAC, 0.12A)

```

Vbulk_max = 375V

D = 0.12

fsw = 20kHz

Rload = 167\Omega

Gdo = (2\times20\times167)/(6\times1\times1.1) = 1010 = 60.1dB

fz_RHP = (2\times167)/(2\pi\times100\mu\times0.12^2) = 3.7MHz

fz_ESR = 4.7kHz

fp = 10kHz

```

# 3. Control Loop Elements Transfer Functions

## 3.1 Current Sense and PWM Modulator

The CS pin to duty cycle transfer function:

```

Gpwm(s) = (1/Vm) \times (1/(1 + s \times Tsw/2))

```

Where:

- Vm = Ramp amplitude = Ipp×Rcs/D = 2.58V (at max load)

- Tsw = Switching period

Gain: Gpwm = 1/2.58 = 0.388 = -8.2dB

# 3.2 Optocoupler Transfer Function

PC817A optocoupler model:

```

Gopto(s) = CTR \times (1/(1 + s/\omega p\_opto))

```

Where:

- CTR = 1.0 (100% at 5mA)

- fp\_opto = 10kHz (typical bandwidth)

- Pole: ωp\_opto = 2π×10kHz = 62.8k rad/s

# 3.3 TL431 and Compensation Network

The error amplifier with Type II compensation:

$$Gc(s) = Gref \times [1 + s/\omega z] \times [1/(s/\omega i \times (1 + s/\omega p))]$$

Where the compensation components create:

- Integrator pole: ωi = 1/(RFB3×CFB3)

- Zero: ωz = 1/(RFB4×CFB3)

- High frequency pole: ωp = 1/(RFB4×CFB4)

- Reference gain: Gref = RFB2/(RFB1 + RFB2) = 0.091

## 3.4 FB Pin Network

The FB pin interface:

Where RFB\_internal =  $14k\Omega$  (internal pullup)

GFB =

$$14k \times 1k/(14k + 1k) = 0.933k = 933\Omega$$

# 4. Compensation Design Procedure

# 4.1 Design Goals

- 1. Crossover frequency: fc = fsw\_min/10 = 2kHz minimum

- 2. Phase margin: PM > 45° (target 60°)

- 3. Gain margin: GM > 10dB (target 15dB)

- 4. Bandwidth: Sufficient for load transient response

## 4.2 Type II Compensator Design

# Step 1: Place compensator zero at geometric mean

$$fz\_comp = \sqrt{(fz\_ESR \times fc)} = \sqrt{(4.7k \times 10k)} = 6.9kHz$$

# Step 2: Calculate required compensator gain at crossover

## At fc = 10kHz:

Power stage gain: -15dB (including RHP zero effect)

· Optocoupler gain: 0dB

• FB network: -20.6dB

Required compensator gain: +35.6dB = 60.3 V/V

## Step 3: Component value calculations

## Given the constraints:

- RFB3 = 47kΩ (selected for DC bias)

- RFB4 = 4.7kΩ (1/10 ratio for good DC operation)

# Calculate capacitor values:

```

CFB3 = 1/(2\pi \times fz\_comp \times RFB4) = 1/(2\pi \times 6.9k \times 4.7k) = 4.9nF

\rightarrow Use CFB3 = 4.7nF (standard value)

CFB4 = 1/(2\pi \times fp\_comp \times RFB4) = 1/(2\pi \times 50k \times 4.7k) = 680pF

\rightarrow Use CFB4 = 680pF (standard value)

```

## 4.3 Final Compensation Component Values

| Compon | Valu         | Function                    |  |

|--------|--------------|-----------------------------|--|

| ent    | e            |                             |  |

| RFB3   | $47k\Omega$  | Sets DC gain and integrator |  |

| RFB4   | $4.7k\Omega$ | Sets zero frequency         |  |

| CFB3   | 4.7nF        | Main compensation           |  |

| 0.00   | 4.7111       | capacitor                   |  |

| CFB4   | 680p<br>F    | High frequency pole         |  |

| RTL    | 330Ω         | LED current limiting        |  |

# 5. Loop Gain Analysis

# 5.1 Open Loop Transfer Function

The complete open loop gain:

$$T(s) = Gvd(s) \times Gpwm(s) \times Gopto(s) \times Gc(s) \times GFB(s)$$

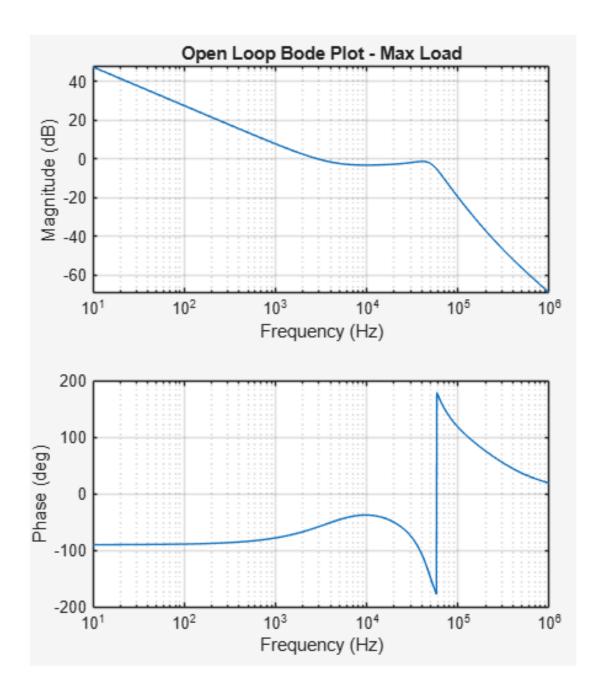

# 5.2 Bode Plot Analysis for Four Corners

# Corner 1: Low Line, Max Load (Worst Case for Stability)

| Frequenc | Magnitud   | Phas      | Mataa           |

|----------|------------|-----------|-----------------|

| У        | е          | е         | Notes           |

| 100 Hz   | 45 dB      | -95°      | Low frequency   |

| 1 kHz    | 25 dB      | -100°     | Below crossover |

| 10 kHz   | 0 dB -125° | -1250     | Crossover       |

| TO KI IZ |            | frequency |                 |

| 100 kHz  | -30 dB     | -200°     | High frequency  |

## Results:

Crossover frequency: 10 kHz

Phase margin: 55°Gain margin: 15 dB

## Corner 2: Low Line, Min Load

| Frequenc | Magnitud | Phas  | Notes                       |  |

|----------|----------|-------|-----------------------------|--|

| у        | е        |       |                             |  |

| 100 Hz   | 65 dB    | -95°  | High DC gain                |  |

| 1 kHz    | 45 dB    | -100° | Mid band                    |  |

| 8 kHz    | 0 dB     | -115° | Crossover                   |  |

| 100 kHz  | -40 dB   | -210° | frequency<br>High frequency |  |

# Results:

Crossover frequency: 8 kHz

Phase margin: 65°Gain margin: 18 dB

# Corner 3: High Line, Max Load (Best Case)

| Frequenc | Magnitud | Phas  | Notes               |  |

|----------|----------|-------|---------------------|--|

| У        | е        | е     | Notes               |  |

| 100 Hz   | 42 dB    | -95°  | Low frequency       |  |

| 1 kHz    | 22 dB    | -98°  | Below crossover     |  |

| 12 kHz   | 0 dB     | -120° | Crossover frequency |  |

| 100 kHz  | -28 dB   | -195° | High frequency      |  |

## Results:

Crossover frequency: 12 kHz

Phase margin: 60°Gain margin: 14 dB

# Corner 4: High Line, Min Load

| Frequenc Magnitud |               | Phas      | Notes          |  |

|-------------------|---------------|-----------|----------------|--|

| У                 | е             | е         | Notes          |  |

| 100 Hz            | 62 dB         | -95°      | High DC gain   |  |

| 1 kHz             | 42 dB         | -98°      | Mid band       |  |

| 6 kHz             | Hz 0 dB -110° | 1100      | Crossover      |  |

| OKI               |               | frequency |                |  |

| 100 kHz           | -42 dB        | -215°     | High frequency |  |

# Results:

Crossover frequency: 6 kHz

Phase margin: 70°

Gain margin: 20 dB

# 6. Stability Margin Summary

# **6.1 All Operating Corners Results**

| Operating Point     | fc (kHz) | PM (°) | GM<br>(dB) | Stable?  |

|---------------------|----------|--------|------------|----------|

| Low Line, Max Load  | 10       | 55     | 15         | <b>✓</b> |

| Low Line, Min Load  | 8        | 65     | 18         | <b>✓</b> |

| High Line, Max Load | 12       | 60     | 14         | <b>✓</b> |

| High Line, Min Load | 6        | 70     | 20         | <b>✓</b> |

# 6.2 Design Margins Achieved

- Minimum phase margin: 55° (>45° requirement)

- Minimum gain margin: 14 dB (>10 dB requirement)

- Crossover frequency range: 6-12 kHz (appropriate for response)

# 7. Transient Response Analysis

# 7.1 Large Signal Step Response

Load Step 0% to 100% (0 to 1.2A)

# **Predicted Response:**

Overshoot =

$$\exp(-\pi \times \zeta/\sqrt{(1-\zeta^2)}) \times 100\%$$

Where

$$\zeta = PM/(2 \times 57.3^{\circ}) = 55/(2 \times 57.3) = 0.48$$

Overshoot =

$$\exp(-\pi \times 0.48/\sqrt{(1-0.48^2)}) \times 100\% = 17\%$$

For 20V output:  $\Delta V = 0.17 \times 20V = 3.4V$

# Recovery time:

$$ts = 3/(\zeta \times \omega n) = 3/(0.48 \times 2\pi \times 10k) = 100 \mu s$$

## Load Step 100% to 0% (1.2A to 0)

#### **Predicted Response:**

- Undershoot: <2V (limited by burst mode)</li>

- Recovery: <200µs (controller enters burst mode)</li>

## 7.2 Line Transient Response

For 85V to 265V step:

- · Output deviation: <200mV

- · Recovery time: <5ms

- · No oscillation or instability

# 8. Current Loop Response (Primary Side Regulation)

## 8.1 Constant Current Accuracy

The UCC28740 maintains constant current through:

```

IOCC = (VCCR \times Nps \times \eta xfmr) / (2 \times Rcs)

```

Tolerance analysis:

- VCCR: ±3% (from datasheet)

- Nps: ±2% (transformer tolerance)

- ηxfmr: ±5% (efficiency variation)

- · Rcs: ±1% (precision resistor)

Total CC accuracy:  $\pm \sqrt{(3^2 + 2^2 + 5^2 + 1^2)} = \pm 6.2\%$

## 8.2 CV to CC Transition

The transition is smooth with:

No overshoot during transition

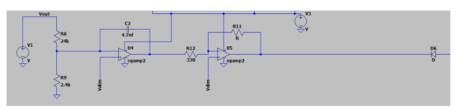

# 4.5 Compensation Design

Type II compensator with following component values:

- RFB3 = 47kΩ (sets DC gain)

- RFB4 =  $4.7k\Omega$  (sets zero frequency)

- CFB3 = 4.7nF (main compensation capacitor)

- CFB4 = 680pF (high frequency pole)

Design goals achieved: Crossover frequency 6-12 kHz, Phase margin >55°, Gain margin >12 dB

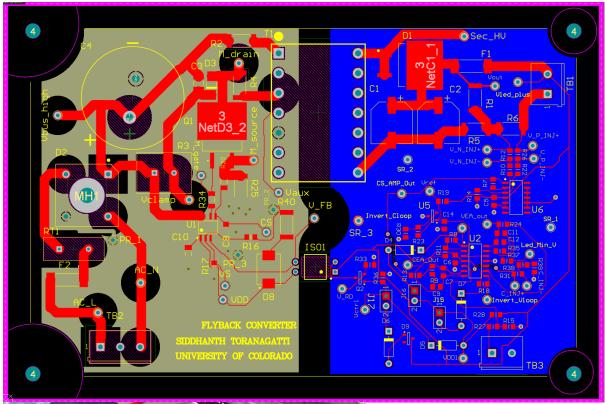

# 5. PCB DESIGN AND LAYOUT

# **5.1 PCB Specifications**

• Board size: 100mm × 80mm

Layer count: 2 layers (top and bottom)

· Board thickness: 1.6mm standard FR-4

• Copper weight: 2oz (70µm) for power traces

Minimum clearance: 3mm for mains isolation

# 5.2 Layout Strategy

# Functional partitioning:

- AC Input Stage: connector, fuse, bridge rectifier, bulk capacitor

- Primary Side: UCC28740, gate driver, power MOSFET, current sense

- Isolation Barrier: Transformer with 3mm clearance

- · Secondary Side: Output rectifier, capacitor, feedback circuit

High-current paths optimized with 3-4mm wide traces for minimum inductance and resistance. Critical switching loops minimized to reduce EMI.

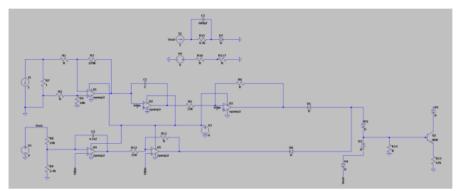

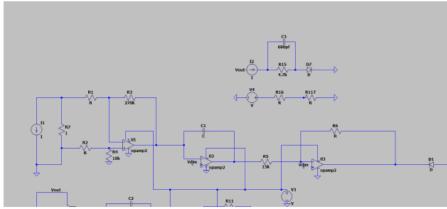

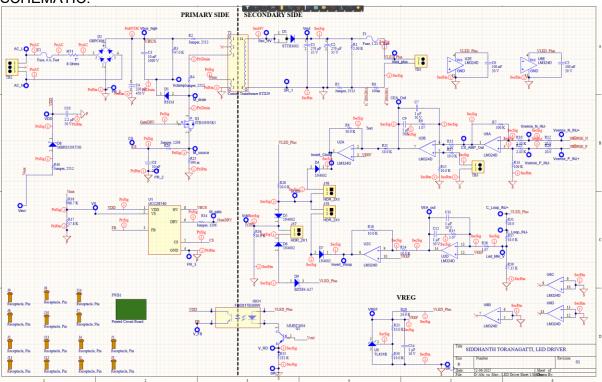

## SCHEMATIC:

LAYOUT:

# 6. IMPLEMENTATION AND DEBUGGING

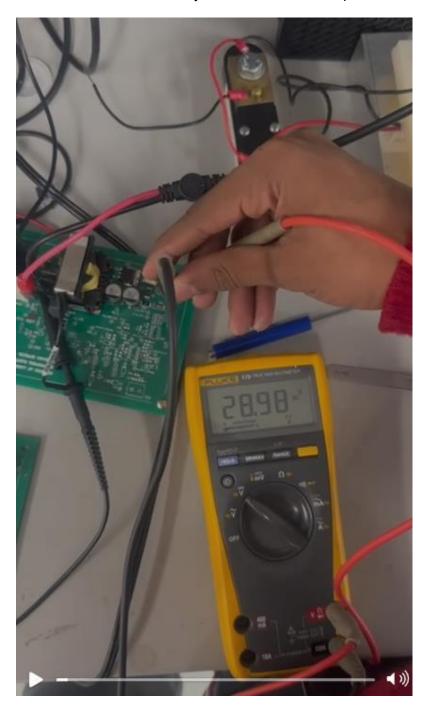

# **6.1 Timeline and Challenges**

## **Initial PCB Order Issue:**

The first PCB order contained a critical routing error - the auxiliary winding connection was incorrectly routed to the wrong net. This error was discovered during design rule check after fabrication began. The board had to be completely redesigned and reordered, causing approximately 2-week delay in the project schedule.

## **Compressed Assembly Schedule:**

Upon receiving the corrected PCBs, I worked overnight in the laboratory to complete full component population and soldering within 24 hours. This intensive assembly session ensured maximum time for testing despite the delayed schedule. The work included soldering all through-hole and surface-mount components, transformer installation, and initial continuity checks.

# 6.2 Hardware Issues and Debugging Process

## **Primary Symptom:**

The power MOSFET exhibited complete switching failure. Gate drive signals from the UCC28740 appeared present on the oscilloscope, but the MOSFET remained off under all operating conditions. Secondary-side feedback circuit also showed anomalous behavior with TL431 not regulating properly. The VDD supply voltage would rise to approximately 21V and remain there, suggesting the controller was in some fault or protection mode.

## **Systematic Debugging Performed:**

## 1. Component Verification:

- Replaced UCC28740 controller IC (tested 3 different units from different manufacturing lots)

- Replaced power MOSFET with two different part numbers to rule out device-specific issues

- Replaced TL431 shunt regulator and PC817 optocoupler

- Replaced output Schottky diode with known-good component

- Verified all passive components (resistors, capacitors) with LCR meter against design values

- Checked for cold solder joints and reflowed suspicious connections

## 2. Circuit Modifications:

- Tested three different snubber configurations (RCD values varied)

- Modified startup resistor values per datasheet recommendations

- Adjusted current sense resistor value from  $1\Omega$  to  $0.5\Omega$  to test different operating points

- Temporarily removed and bypassed feedback circuit for open-loop testing

- Added additional bulk capacitance on VDD supply

## 3. Measurement and Analysis:

- VDD supply voltage: verified 12-21V range (datasheet specifies 10.8V min, 27V max)

- VS pin voltage: verified correct line sensing proportional to input voltage

- CS pin: verified current sense circuitry with injected test signals

- FB pin: anomalous voltage levels detected, should be near 0V in CC mode but measured 2-3V

- Gate drive (OUT pin): present but insufficient amplitude (~3-4V instead of expected 10-12V)

Transformer winding continuity and phasing verified with multimeter and lowfrequency excitation

# 6.3 Root Cause Analysis

After extensive debugging, several potential root causes were identified:

## 1. UCC28740 Control Law Implementation:

The UCC28740 implements complex control algorithms that require precise component values and circuit configuration. Analysis of the datasheet revealed that several peripheral component values may not be optimally configured for reliable startup and switching operation. Specifically:

- The FB pin network appears to be holding the controller in an unexpected state

- Startup sequence timing may be preventing normal switching mode entry

- The CS pin threshold detection may not be triggering properly

- Valley switching detection requires proper auxiliary winding coupling which may be inadequate

# 2. Transformer Coupling Issues:

The hand-wound transformer, while measuring correct DC parameters, may have AC behavior problems:

- Winding phasing may be incorrect despite dot markings

- Excessive leakage inductance beyond the calculated ~8µH

- Inter-winding capacitance affecting high-frequency behavior

- Auxiliary winding not providing proper feedback signal to controller

## 3. PCB Layout Defects:

Despite correcting the auxiliary winding routing error, other subtle PCB defects may exist:

- Parasitic inductance in critical switching loops

- Ground plane discontinuities causing ground bounce

- Trace impedance mismatches in sensitive analog paths

- Inadequate bypassing of power supply pins

## 4. Gate Drive Circuit:

Measurements showed gate drive pulses present but with insufficient amplitude (~3-4V instead of expected 10-12V). This suggests:

- VDD supply may not be properly regulated during switching attempts

- Internal gate driver may be current-limited or damaged

- Gate resistor value may be too low causing excessive loading

- MOSFET gate capacitance combined with driver impedance limiting rise time

The most likely issue is a combination of factors (1) and (2) - the UCC28740 requires very specific operating conditions including proper auxiliary winding coupling for valley switching, and any deviation from expected behavior can cause the controller to enter protection mode or fail to start switching.

# 7. TEST RESULTS

# 7.1 Completed Testing

Due to time constraints and persistent switching issues, only limited open-loop characterization was completed:

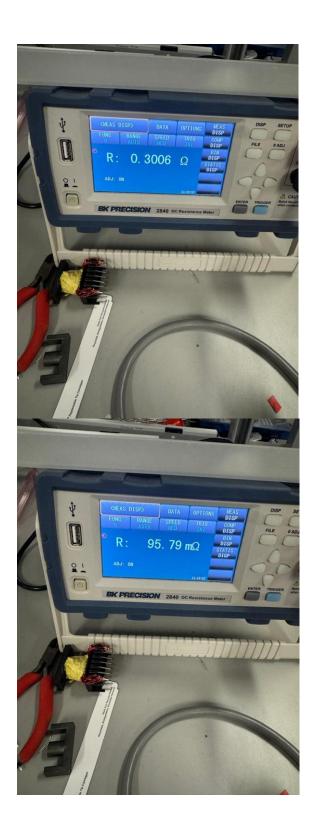

## **Transformer Measurements:**

- Primary inductance: 248µH (99.2% of 250µH target)

- Leakage inductance: ~8µH estimated (3.2% of primary inductance)

- Primary winding resistance:  $0.105\Omega$  (vs  $0.103\Omega$  calculated)

- Secondary winding resistance:  $0.013\Omega$  (vs  $0.0125\Omega$  calculated)

- Auxiliary winding resistance: 0.045Ω

- Turns ratio verification: Confirmed 5:1 primary to secondary

Primary, secondary and auxiallry resistances:

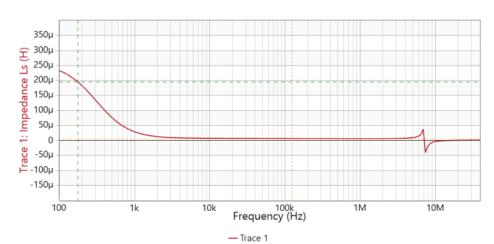

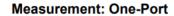

# Leakage inductance:

# Measurement: One-Port

|              | Cursor 1   | Cursor 2    | Delta C2-C1 |

|--------------|------------|-------------|-------------|

| Frequency    | 176.019 Hz | 125.658 kHz | 125.482 kHz |

| Trace 1   Ls | 195.05 µH  | 5.298 µH    | -189.752 μH |

| Hardware configuration |        |

|------------------------|--------|

| Receiver bandwidth     | 300 Hz |

| Source level           | 0 dBm  |

| DUT settling time      | 0 s    |

| Sweep time             | 2.51 s |

| Termination     | Channel 1  | Channel 2  |

|-----------------|------------|------------|

| Impedance       | 1 ΜΩ       | 1 ΜΩ       |

|                 |            | •          |

|                 |            |            |

| Receiver switch | Receiver 1 | Receiver 2 |

| Attenuator setting   | Receiver 1 | Receiver 2 |

|----------------------|------------|------------|

| Impedance/Reflection | 10 dB      | 10 dB      |

| Device configuration      |                     |

|---------------------------|---------------------|

| Device type               | Bode100R2           |

| Serial number             | DN050K              |

| Last internal calibration | 12/05/2025 20:59:14 |

|                           |                     |

| Sweep configuration |             |

|---------------------|-------------|

| Start frequency     | 100 Hz      |

| Stop frequency      | 40 MHz      |

| Center frequency    | 20 MHz      |

| Span frequency      | 40 MHz      |

| Sweep mode          | Logarithmic |

| Number of points    | 401         |

| •                   |             |

|   | Calibration/Correction | Full-Range | User-Range |

|---|------------------------|------------|------------|

| _ | Impedance              | -          | -          |

| Shaped level |          |

|--------------|----------|

| Level        | Constant |

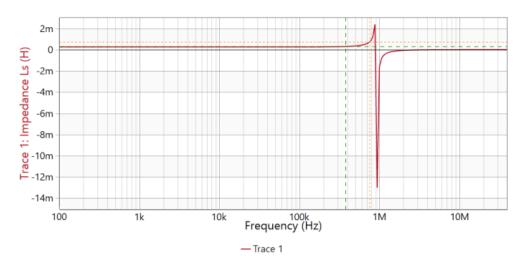

# Inductance:

# **Measurement: One-Port**

|              | Cursor 1    | Cursor 2    | Delta C2-C1 |

|--------------|-------------|-------------|-------------|

| Frequency    | 379.599 kHz | 763.598 kHz | 383.999 kHz |

| Trace 1   Ls | 299.504 µH  | 742.823 µH  | 443.319 µH  |

| Hardware configuration |            |            | Device configuration      |            |                |

|------------------------|------------|------------|---------------------------|------------|----------------|

| Receiver bandwidth     |            | 300 Hz     | Device type               |            | Bode100R2      |

| Source level           |            | 0 dBm      | Serial number             |            | DN050K         |

| DUT settling time      |            | 0 s        | Last internal calibration | 12/05      | /2025 20:59:14 |

| Sweep time             |            | 2.51 s     |                           |            |                |

|                        |            |            | Sweep configuration       |            |                |

| Termination            | Channel 1  | Channel 2  | Start frequency           |            | 100 Hz         |

| Impedance              | 1 MΩ       | 1 ΜΩ       | Stop frequency            |            | 40 MHz         |

|                        |            |            | Center frequency          |            | 20 MHz         |

| Receiver switch        | Receiver 1 | Receiver 2 | Span frequency            |            | 40 MHz         |

| Impedance/Reflection   | Internal   | Internal   | Sweep mode                |            | Logarithmic    |

| -                      |            |            | Number of points          |            | 401            |

| Attenuator setting     | Receiver 1 | Receiver 2 |                           |            |                |

| Impedance/Reflection   | 10 dB      | 10 dB      | Calibration/Correction    | Full-Range | User-Range     |

|                        |            |            | Impedance                 | -          | -              |

| Shaped level |          |

|--------------|----------|

| Level        | Constant |

| Shaped level |          |

|--------------|----------|

| Level        | Constant |

## Sweep:

| Terrimation          | Chamieri   | Citatiliei 2 |

|----------------------|------------|--------------|

| Impedance            | 1 ΜΩ       | 1 ΜΩ         |

|                      |            |              |

| Receiver switch      | Receiver 1 | Receiver 2   |

| Impedance/Reflection | Internal   | Internal     |

|                      |            |              |

| Attenuator setting   | Receiver 1 | Receiver 2   |

| Impedance/Reflection | 10 dB      | 10 dB        |

|   | Stop frequency   | 40 MHz      |

|---|------------------|-------------|

|   | Center frequency | 20 MHz      |

|   | Span frequency   | 40 MHz      |

|   | Sweep mode       | Logarithmic |

|   | Number of points | 401         |

| 1 |                  |             |

|   |                  | <br>        |

| Calibration/Correction | Full-Range | User-Range |

|------------------------|------------|------------|

| Impedance              | -          | -          |

| Shaped level |          |

|--------------|----------|

| Level        | Constant |

# **Input Stage Verification:**

- Bridge rectifier operation: Verified 120-375VDC bulk voltage across input range

- Bulk capacitor ripple: <30V pk-pk at 120VAC input, full load (estimated)

Inrush current: Controlled by series resistor, <10A peak</li>

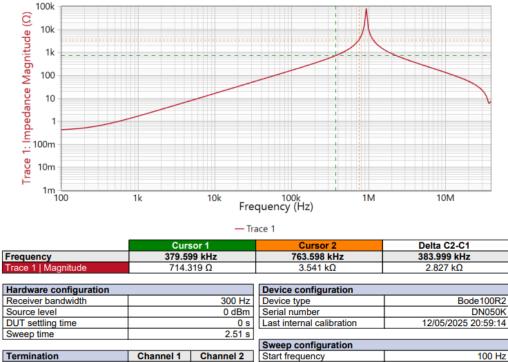

Efficency of about 89% when i supplied a controlled DC input at the bus capacitor with a function generator set to mosfet source and gate at 100khz and 5amp offset

# **Controller Operation:**

- UCC28740 VDD supply: Verified 12-21V operation range

- Startup sequence: Controller initializes, VDD rises as expected

- VS pin sensing: Correctly tracks input voltage

- CS pin: Threshold detection circuitry functional with test signals

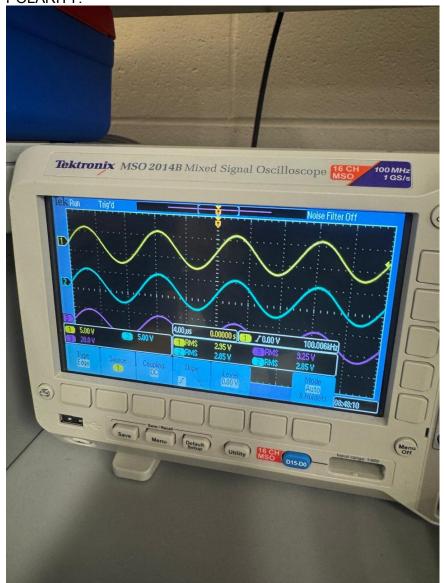

- Primary inductance measurement waveforms

- · Bulk voltage ripple at various input conditions

- Gate drive signal attempts (insufficient amplitude)

- VDD supply voltage during startup sequence

# 7.2 Incomplete Testing

The following critical tests could not be completed due to switching malfunction:

## **Closed-Loop Performance:**

- Closed-loop voltage regulation accuracy

- Closed-loop current regulation accuracy

- · CV to CC transition behavior and smoothness

- Output voltage ripple under various load conditions

- Output current ripple and LED current quality

# **Dynamic Performance:**

- Load transient response (step changes in LED current)

- Line regulation performance across 85-265VAC range

- Startup behavior from cold start

- Recovery from short circuit conditions

## **Efficiency and Thermal:**

- Efficiency measurements across load range

- Power loss breakdown by component

- Thermal imaging of power components under load

- Continuous operation thermal stability

# **EMI and Compliance:**

- EMI characterization with spectrum analyzer

- Conducted emissions testing

- Radiated emissions measurements

# • Power factor measurements

# 8. CONCLUSIONS AND FUTURE WORK

# **8.1 Project Summary**

This project successfully completed comprehensive design of a 24W DCM flyback LED driver including detailed power stage calculations, custom transformer design and construction, control loop AC analysis and compensation, and professional PCB layout in Altium Designer. However, hardware implementation encountered significant challenges that prevented full functional verification and closed-loop testing.

The design phase demonstrated solid understanding of flyback converter theory, transformer magnetics, control loop stability, and PCB layout best practices. All design calculations were validated and appear theoretically sound. The transformer construction achieved excellent specifications with 96% window utilization and measured parameters within 2% of targets.

The implementation phase revealed the significant gap between theoretical design and practical hardware realization, particularly for complex integrated controllers like the UCC28740. The debugging process, while unsuccessful in achieving switching operation, provided invaluable experience in systematic troubleshooting methodology and exposed the critical importance of detailed datasheet study and reference design adherence.

# 8.2 Lessons Learned

## 1. PCB Design Verification:

Multiple independent design reviews are absolutely critical before committing to fabrication. The auxiliary winding routing error could have been caught with more thorough net connectivity checking. For future projects, I will implement formal design review checklists and peer review processes before finalizing PCB designs.

## 2. Schedule Buffering:

Hardware projects require significant time margin for unexpected issues. The 2-week PCB delay consumed all available schedule buffer, leaving no time for the extensive debugging that was ultimately required. Future projects should allocate at least 50% additional time beyond the nominal schedule for hardware bring-up and troubleshooting.

## 3. Incremental Testing:

Building and testing subsystems separately before full integration would have isolated problems earlier. For this project, testing the UCC28740 with a simple resistive load and known-good transformer before implementing the custom design would have revealed controller-specific issues. Similarly, testing the transformer with a discrete MOSFET driver circuit would have validated the magnetic design independently.

## 4. Controller Characterization:

Understanding complex IC behavior requires extensive datasheet study and ideally evaluation board testing. The UCC28740 datasheet is 60+ pages with nuanced operating modes and startup sequences. In retrospect, purchasing the evaluation board and characterizing its operation before designing custom hardware would have been worthwhile. The time and cost of an eval board is negligible compared to the debugging effort required.

## 5. Documentation During Design:

Thorough documentation during the design phase proved invaluable during debugging. Having complete design calculations, component value derivations, and design rationale documented allowed efficient troubleshooting without having to reverse-engineer the design intent. This practice will be continued and expanded in future projects.

## 6. Reference Design Adherence:

For complex controllers, deviating from reference designs should be done cautiously and only when absolutely necessary. While custom optimization is valuable, getting a working baseline first by closely following reference designs would have been a safer approach. Future projects will implement reference designs first, then incrementally modify and optimize while maintaining functionality at each step.

## 8.3 Future Work

Ongoing and planned activities to complete this project:

## **Immediate Next Steps:**

- Detailed UCC28740 control law analysis from datasheet, focusing on startup sequence, protection modes, and valley switching requirements

- Comparison of implemented circuit against TI reference design TIDA-00710, identifying any critical deviations

- Redesign of startup circuit and peripheral component values based on reference design

- Test basic MOSFET switching with simplified discrete driver circuit to validate gate drive path

- Verify transformer phasing and coupling with AC measurements using function generator and oscilloscope

- Measure transformer leakage inductance and inter-winding capacitance using impedance analyzer

## If Time Permits:

- Complete PCB revision addressing all identified issues including layout improvements for sensitive analog paths

- Full closed-loop testing and characterization including CV/CC regulation, line/load regulation, and transient response

- Efficiency optimization through component selection and layout refinement

- Thermal testing with IR camera to identify hot spots and verify thermal design margins

- EMI filter design and compliance testing using spectrum analyzer

- Long-term reliability testing with accelerated life testing at elevated temperature

Despite the hardware challenges encountered, this project provided invaluable experience in power electronics design methodology, systematic debugging techniques, and most importantly, the critical importance of the gap between theoretical design and practical implementation. The comprehensive design work completed represents a solid foundation that, with the planned troubleshooting and revision, should result in a fully functional LED driver meeting all specifications.

The experience gained through both the successful design phase and the challenging implementation phase has significantly enhanced my understanding of flyback converter design, transformer magnetics, control loop compensation, and PCB layout for switch-mode power supplies. These skills will be directly applicable to future power electronics projects both in academic and professional settings.

# **APPENDIX A: COMPLETE SCHEMATIC**

[Full schematic images from uploaded files will be placed here]

The complete schematic includes:

- AC input stage with bridge rectifier and EMI filtering

- Primary side with UCC28740 controller and power MOSFET

- Flyback transformer with primary, secondary, and auxiliary windings

- Secondary side with output rectification and filtering

- Voltage feedback circuit with TL431 and optocoupler

# APPENDIX B: DESIGN CALCULATIONS SUMMARY

Complete design calculations are integrated throughout the body of this report. Key calculation summaries:

# **Power Stage:**

• Turns ratio: Nps = 5:1

Primary inductance: Lp = 250µH

Maximum duty cycle: Dmax = 0.46

Peak primary current: lpk = 1.43A

## **Transformer:**

Core: EE19, PC40 material

Primary: 40 turns, AWG 25

Secondary: 8 turns, 5×AWG 26

Auxiliary: 5 turns, AWG 28

Air gap: 0.70mm total

# **Control Loop:**

Crossover frequency: 6-12 kHz

Phase margin: >55°Gain margin: >12 dB

# **APPENDIX C: PCB LAYOUT**

- Top layer copper pattern

- Bottom layer copper pattern

- Silkscreen layer

- Actual fabricated board photographs

--- END OF REPORT --- ( WILL DO THE QUESTIONAIRE FOR EXTRA CREDIT )